# Practical Workbook CS-205/CS-251 Logic Design & Switching Theory (EE / SCIT / SE)

|          |     | \ |

|----------|-----|---|

| Name     | :   | ) |

| Year     | :   |   |

| Batch    | :   |   |

| Roll No  | :   |   |

| Departme | nt: |   |

# Dept. of Computer & Information Systems Engineering NED University of Engineering & Technology

# **INTRODUCTION**

The logic designing area covers the digital building blocks, tools, and techniques in the design of computers and other digital systems. Logic Design and Switching Theory covers a variety of basic topics, including switching theory, combinational and sequential logic circuits, and memory elements.

In this Practical Workbook, laboratory sessions based on both combinational and sequential logic are covered. The lab sessions fall into two categories:

- 1. Hardware implementation and IC testing. It covers combinational and sequential circuit building on a bread board or logic trainer board, and testing of various MSI ICs including registers and different types of counters.

- Logic circuit simulation on CAD software Electronics Workbench (EWB). EWB is excellent simulation software, where circuits can be designed and tested before physical implementation. Various laboratory sessions of this workbook provide activities and exercises on EWB.

All laboratory sessions of this workbook incorporate brief theoretical backgrounds, as details may be covered in the respective theory classes. Exercises / activities are included with almost all the sessions for the students to practice.

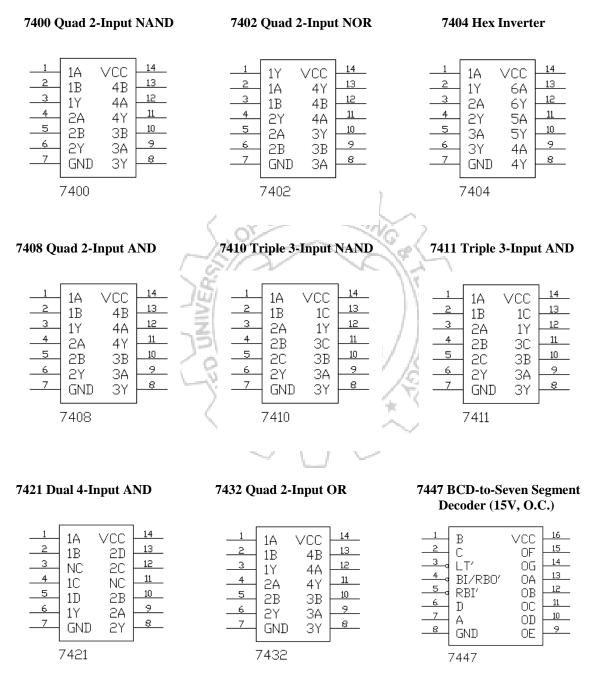

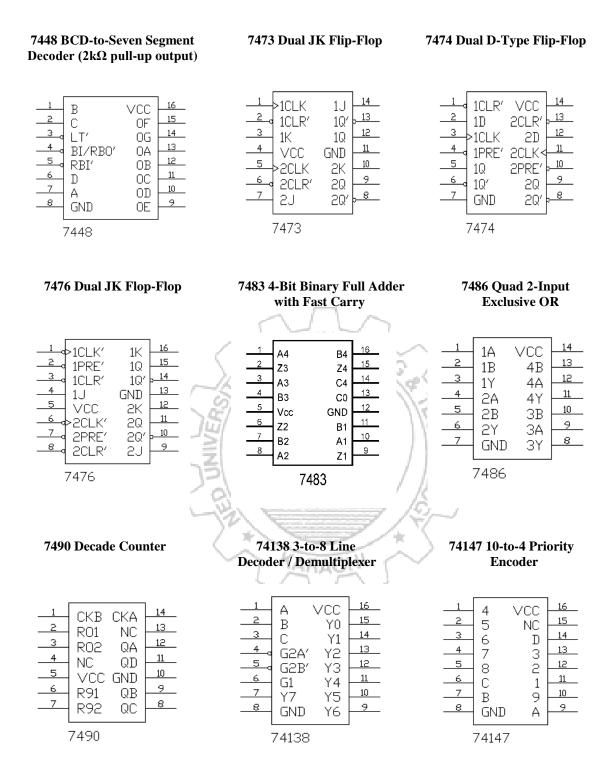

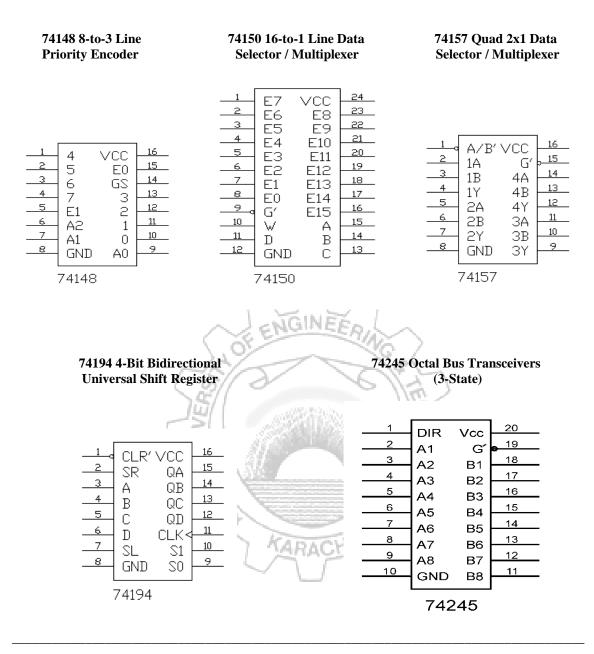

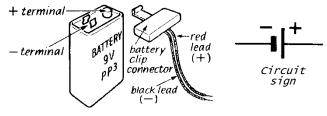

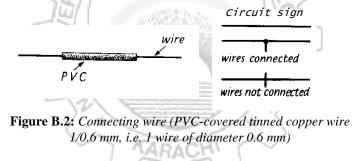

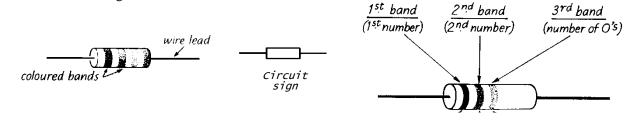

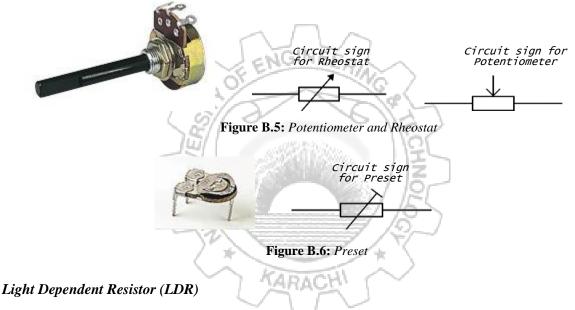

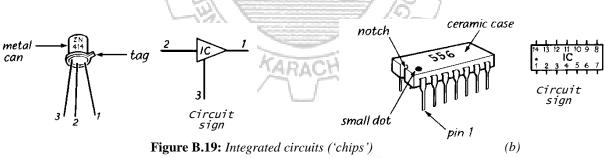

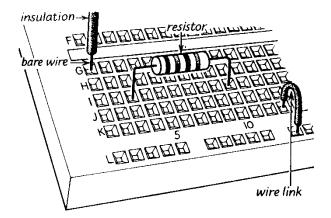

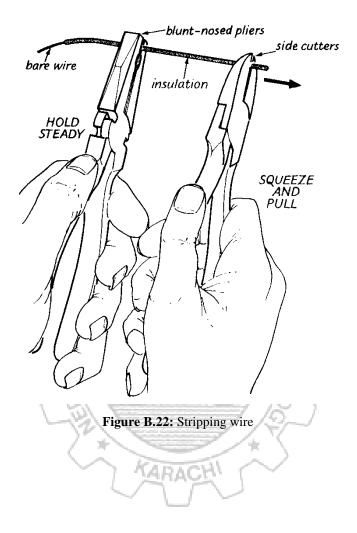

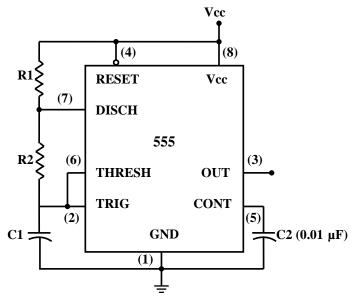

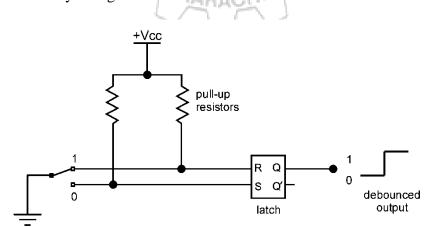

Three appendices are also included in this workbook. The first one provides pin diagrams for all the ICs required for the laboratory work provided in this workbook. It will help the students in preparing the pin diagrams for the circuits. Second appendix covers hardware equipment /components other than ICs that are commonly required in building circuits / mini projects. Third appendix discusses generation of square wave via 555 timer IC and a hardware debouncing circuit for mechanical switches as such switches are extensively used for input purpose in logic circuits.

# PREREQUISITES

The students coming for the lab sessions of Logic Design & Switching Theory, should have a personal hardware kit containing the following items:

- 1 Power supply (preferably student made).

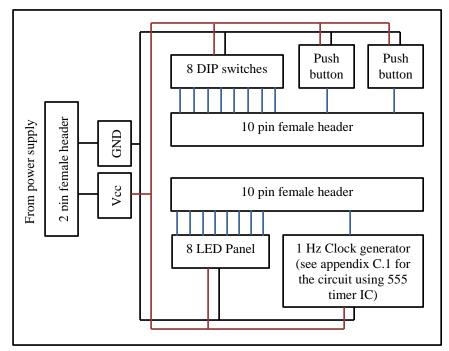

- 2 An Input-Output panel as shown in figure A (preferably student made).

- 3 2-3 ICs of each of the following type:7400, 7404, 7408, 7432, 7447, 7473, 7474, 7476, 7486

- 4 1 IC of each of the following type:7490, 74138, 74148, 74150, 74194, any EEPROM

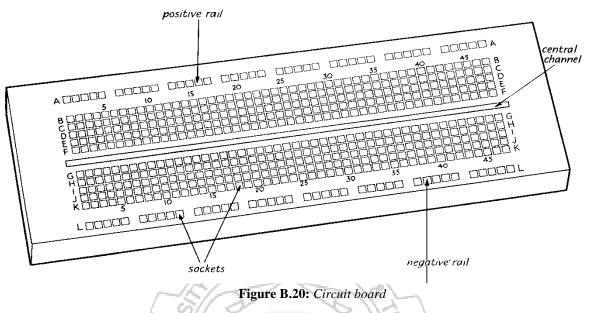

- 5 Breadboard

- 6 Connecting wires

Figure A: Input-Output panel

# CONTENTS

| Lab Session No | . Objective                                                                                                                             | Page No |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------|

| 1              | Experimenting with logic gates, implementing the circuit on bread board and observing output for various combinations of inputs.        | 1       |

| 2              | Working with Electronics Workbench.                                                                                                     | 5       |

| 3              | Simplifying and implementing the given logic expression in hardware and realizing its NAND equivalent.                                  | 8       |

| 4              | Implementing half and full adder circuits.                                                                                              | 10      |

| 5              | Simulating a 4-bit parallel adder on Electronics Workbench.                                                                             | 12      |

| 6              | Experimenting with digital decoder IC                                                                                                   | 14      |

| 7              | Experimenting with digital multiplexer IC.                                                                                              | 16      |

| 8              | Experimenting with encoder and seven segment display driver ICs.                                                                        | 18      |

| 9              | Testing different modes of JK flip flop, and implementing a modulo-4 asynchronous up-counter using JK flip flops.                       | 21      |

| 10             | Experimenting with decade counter IC.                                                                                                   | 25      |

| 11             | Designing and simulating the second section of a digital clock.                                                                         | 27      |

| 12             | Experimenting with bidirectional universal shift register IC.                                                                           | 29      |

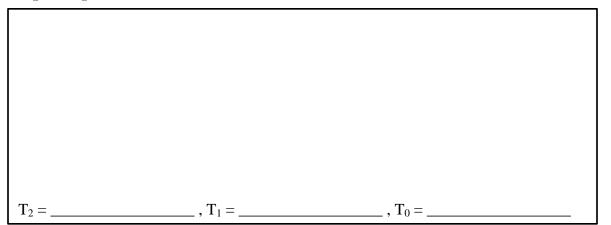

| 13             | Designing and implementing a 3-bit even sequence synchronous up counter using T flip flops.                                             | 31      |

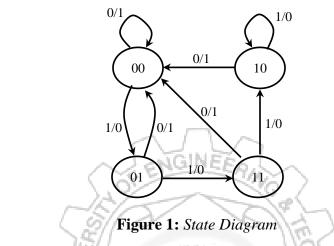

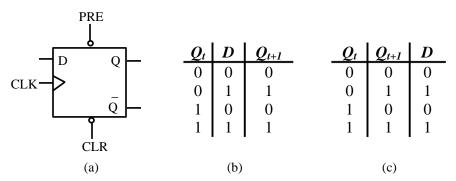

| 14             | Designing and implementing synchronous sequential circuit for the given state diagram using D flip-flop.                                | 34      |

|                | Appendix A<br>Pin diagrams of the ICs required for the laboratory sessions.                                                             | 38      |

|                | Appendix B<br>Common components (beside logic ICs) used in building circuits.                                                           | 41      |

|                | <ul><li>Appendix C</li><li>C.1 Clock generation using 555 timer IC.</li><li>C.2 Debouncing circuitry for mechanical switches.</li></ul> | 51      |

# Lab Session 01

#### **OBJECTIVE**

Experimenting with logic gates, implementing the circuit on bread board and observing output for various combinations of inputs.

#### **COMPONENTS REQUIRED**

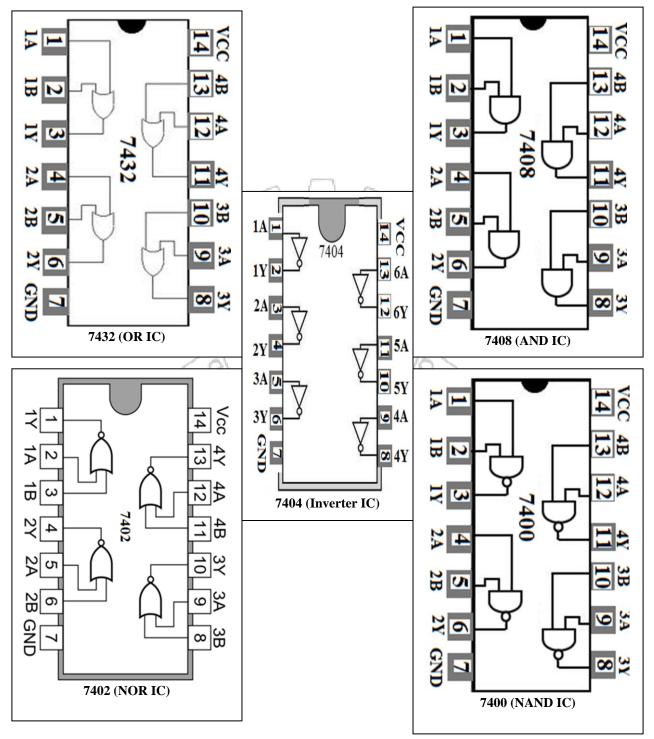

- Bread board, 5 V power supply, multimeter, logic probe (or LEDs with resistors), wires and the following ICs:

- 7408 quad 2 input AND gate

- 7432 quad 2 input OR gate

- 7404 hex inverter

- 7400 quad 2 input NAND gate

- 7402 quad 2 input NOR gate

#### THEORY

#### Logic Gates

Logic gates are the fundamental building blocks of digital systems. These devices are able to make decisions, in the sense that they produce one output level when some combinations of input levels are present and a different output when other combinations are applied; hence given the name Logic Gates.

ENGINEE

The two levels produced by digital circuitry are referred to variously as HIGH and LOW, TRUE and FALSE, ON and OFF, or simply 1 and 0.

There are only three basic gates: AND, OR and NOT. The other gates are merely combinations of these basic gates.

- 1. The AND Gate An AND gate's output is 1 if and only if all its inputs are 1. If A and B are two inputs to an AND gate then output, F of the gate is given as: F = A.B

- 2. The OR Gate An OR gate's output is 1 if at least one of its input is 1. If A and B are two inputs to an OR gate then output, F of the gate is given as: F = A+B

- 3. The NOT Gate (Inverter) Its output is 1 when its input is 0 and its output is 0 when the input is 1; i.e. it complements a digital variable. If A is the input to a NOT gate then output, F of the gate is given as:  $F = \overline{A}$

- 4. The NAND Gate Its output is 1 if at least one of its inputs is 0. This gate performs the same logic as an AND gate followed by an inverter. If <u>A</u> and B are two inputs to a NAND gate then output, F of the gate is given as: F = A.B

5. The NOR Gate - The output of a NOR gate is 1 if and only if all its inputs are 0. This gate performs the same logic function as an OR gate followed by an inverter. If A and B are two inputs to a NAND gate then output, F of the gate is given as: F = A+B

All the above gates have one output and two or more inputs except the NOT gate, which has only one input.

#### **INTERNAL IC DIAGRAMS**

Figure 1: ICs Internal Diagrams

# **PROCEDURE**

- 1. Set the power supply to 5V. With the help of a multimeter check the voltage at the output knobs of the power supply.

- 2. Connect wires, long enough to reach the bread board, with the two knobs of the power supply. Again using multimeter, check the voltage at the non-connected end of the wires.

- 3. Insert the 7408 quad 2 input AND gate IC on to the bread board and make supply and ground connections by joining 5V wire to pin # 14 and 0V wire to pin # 7.

- 4. Consult IC's internal connection diagram for input and output pins of the first AND gate. Connect input pins to logic 0 (0V) and observe the output using LED or logic probe.

- 5. Try different combinations of logic levels at the two inputs. Again observe the output.

- 6. Repeat the last two steps for all other gates of the same IC. Record the observations.

- 7. Repeat this procedure for all other ICs.

# **OBSERVATIONS**

**AND Gate**

| Α       | В      | Expected Output | Observed Output |

|---------|--------|-----------------|-----------------|

| 0       | 0      | ILA             |                 |

| 0       | L J CN | GINEROL         |                 |

| 1       | 0      |                 |                 |

| 1       | _14/   | - Not           |                 |

| OR Gate | 5312   | ell'a           | 3               |

**OR** Gate

|   | 1611 | Line Mar                        |

|---|------|---------------------------------|

| Α | B    | Expected Output Observed Output |

| 0 |      |                                 |

| 0 |      |                                 |

| 1 | 0    |                                 |

| 1 |      |                                 |

**NOT Gate**

| A | Expected Output | Observed Output |

|---|-----------------|-----------------|

| 0 |                 |                 |

| 1 |                 |                 |

KADACHI

NAND Gate

| Α | В | Expected Output | Observed Output |

|---|---|-----------------|-----------------|

| 0 | 0 |                 |                 |

| 0 | 1 |                 |                 |

| 1 | 0 |                 |                 |

| 1 | 1 |                 |                 |

**NOR Gate**

| Α | В | Expected Output | Observed Output |

|---|---|-----------------|-----------------|

| 0 | 0 |                 |                 |

| 0 | 1 |                 |                 |

| 1 | 0 |                 |                 |

| 1 | 1 |                 |                 |

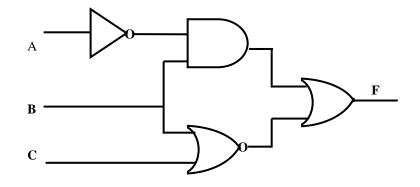

# FINDING EXPRESSION FOR GIVEN LOGIC DIAGRAM

#### LOGIC DIAGRAM

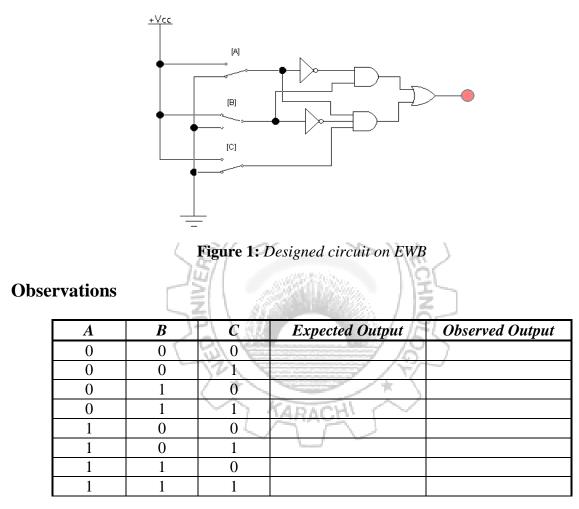

#### Figure 2: Logic Diagram

NGINER

#### PROCEDURE

- 1. Set the power supply to 5V. With the help of a multimeter check the voltage at the output knobs of the power supply.

- 2. Connect wires, long enough to reach the bread board, with the two knobs of the power supply. Again using millimeter, check the voltage at the non-connected end of the wires.

- 3. Insert ICs on the bread board and make their supply and ground connections.

- 4. As given in the logic diagram, make connections using wires and gates in the ICs.

- 5. Apply different combinations at the three inputs and observe the output.

# **OBSERVATIONS**

Logic expression for the given logic diagram:

| Α | В | C   | Expected Output | <b>Observed Output</b> |

|---|---|-----|-----------------|------------------------|

| 0 | 0 | -0/ | TV.             |                        |

| 0 | 0 | 1   |                 |                        |

| 0 | 1 | 0   |                 |                        |

| 0 | 1 | 1   |                 |                        |

| 1 | 0 | 0   |                 |                        |

| 1 | 0 | 1   |                 |                        |

| 1 | 1 | 0   |                 |                        |

| 1 | 1 | 1   |                 |                        |

索

# Lab Session 02

# **OBJECTIVE**

Working with Electronics Workbench

# **ELECTRONICS WORKBENCH - EWB**

Electronics Workbench is a computer aided design tool that provides you with all the components and instruments necessary to create board-level designs. It has complete mixed analog and digital simulation and graphical waveform analysis, allowing you to design your circuit and then analyze it using different simulated instruments and analysis options. It is fully integrated and interactive, thus you can change your circuits quickly, allowing fast and repeated what-if analysis.

RINEFE

Electronics Workbench provides the following kind of components:

- Sources parts bin (*AC voltage source, Vcc source, ground, battery, etc*)

- Basic parts bin (resistors, capacitors, transformers, switches, etc)

- Diodes parts bin

- Transistors parts bin

- Analog ICs parts bin (op-amps, etc)

- Mixed ICs parts bin (ADCs, DACs, 555 timers, etc)

- Digital ICs parts bin (AND, OR, adders, multiplexers, etc)

- Indicators parts bin (voltmeter, ammeter, probe, displays, etc) -

- Controls parts bin (voltage differentiator, multiplier, etc)

- Instruments parts bin (multimeter, oscilloscope, function generator, etc)

- Miscellaneous parts bin (write data, textbox, etc)

- Write data: This component allows you to save simulation results as an ASCII file.

- Text Box: Use this to add descriptive text anywhere in a circuit.

# DESIGNING LOGIC CIRCUIT FOR A GIVEN LOGIC EXPRESSION

Given Logic Expression:  $F = \overline{A}.B + A.\overline{B}.C$

# Procedure

- 1. From *Logic Gates Parts Bin*, drag and drop the required logic gates on the design area. Use *Component Properties* dialog box to customize these gates.

- 2. Connect the terminal of these gates according to the given expression. Use additional connectors form the *Basic Parts Bin* if more than one wire needs to be connected at a single node.

- 3. Drag and drop a *probe* from *Indicators Parts Bin*. Use *Component Properties* dialog box to customize the color and other properties of the probe. Connect this probe at the output terminal of the circuit to indicate results.

- 4. Select four *switches* form *Basic Parts Bin*. Specify the key that controls the switch by typing its name in the *Value* tab of the *Component Properties* dialog box. For example, if you want the switch to close or open when digit '1' is pressed, type 1 in the *Value* tab, then click *OK*. Assign different keys to all the switches.

- 5. Connect the output terminals of the switches to each of the circuit inputs A, B, and C.

- 6. Drag and drop Vcc and Ground form the Sources Parts Bin.

- 7. Connect Vcc terminal to one end and Ground terminal to the other end of all the switches.

- 8. Label the circuit properly using *text boxes* found in the *miscellaneous parts bin*.

- 9. Run the circuit using the *Activate Simulation* switch. Use the keys you have assigned to the switches to toggle them between *Vcc* and Ground connections, thus providing 1 or 0 respectively to the inputs. Record the results as indicated by the probe for all possible combinations of 1s and 0s at the inputs.

### **EWB** Circuit

#### **USING LOGIC CONVERTER**

Logic converter can be used to derive truth table and logic expression for a given logic circuit or vice versa, i.e. if a logic circuit is expressed in any one of the three ways, other two can be directly obtained using the logic converter.

From the Instruments Parts Bin, drag and drop Logic Converter on the design area. Double click the Logic Converter to reveal Logic Converter dialog box. This dialog box shows various conversion options between truth table, logic expression and logic circuit.

#### Finding truth table and logic expression for a given logic circuit

- 1. Create any arbitrary logic circuit on the design area.

- 2. Attach the input terminals of the logic converter to the input points in the circuit.

- 3. Connect the single output of the circuit to the output terminal on the logic converter icon.

- 4. Click the Circuit to Truth Table button. The truth table appears in the logic converter's display.

- 5. To convert this truth table to a Boolean expression, click the Truth Table to Boolean Expression button. The Boolean expression will be displayed at the bottom of the logic converter.

# Creating logic circuit and truth table for a given logic expression

- 1. Enter the given logic expression in the edit box found at the end of the Logic converter dialog box. Use 'to represent invert of a variable. For example,  $\overline{A}$  is written as A'.

- 2. Click the Boolean Expression to Truth Table button. The truth table appears in the logic converter's display.

- 3. Now click the Boolean Expression to Circuit button. This creates the logic circuit for the given expression in the design area. Label the diagram if needed.

# Creating logic circuit and finding logic expression for a given truth table

- 1. Click desired number of input channels from A to H, across the top of the logic converter. The display area below the terminals fills up with the necessary combinations of ones and zeros to fulfill the input conditions. The values in the output column on the right are initially set to 0.

- 2. Edit the output column to specify the desired output for each input condition. To change an output value, select it and type a new value: 1, 0 or x. An x indicates a don't care condition.

- 3. To convert this truth table to a Boolean expression, click the Truth Table to Boolean Expression button. The Boolean expression will be displayed at the bottom of the logic converter.

- 4. Simplify the expression by clicking the Simplify button.

- 5. Now click the Boolean Expression to Circuit button. This creates the logic circuit for the given expression in the design area.

# EXERCISE

1. Create a neat pin diagram (using TTL ICs) for the logic expression  $F = \overline{A}.B + A.\overline{B}.C$ . Test the output and attach hard copy of the diagram here.

# Lab Session 03

# **OBJECTIVE**

Simplifying and implementing the given logic expression in hardware and realizing its NAND equivalent.

# **COMPONENTS REQUIRED**

- Digital logic trainer board or the following components: Bread board, 5 V - Power Supply, Multimeter, LEDs with Resistors, Switches

- 2. Logic probe

- 3. Connecting wires

- 4. Following ICs and their datasheets or pin configurations:

- 5. 7400 quad 2 input NAND gate

- 6. 7404 hex inverter

- 7. 7408 quad 2 input AND gate

- 8. 7432 quad 2 input OR gate

# GIVEN LOGIC EXPRESSION NGIN

F(A,B,C,D) =(0,2,3,7,8,10,11,14,15)

# PROCEDURE

- 1. Use Karnaugh map to reduce the given function.

- 2. Draw the circuit diagram for the obtained reduced function.

- 3. Implement the reduced circuit using digital ICs on a bread board (refer to appendix A for IC pin configurations) and record the observations.

- 4. Find NAND realization for the simplified circuit.

- 5. Implement the all NAND circuit using digital ICs on a bread board (refer to appendix A for the pin diagram) and verify the observations taken in step 3.

# **REDUCTION OF LOGIC EXPRESSION**

Reduced logic expression comes out to be: \_

# LOGIC DIAGRAM (REDUCED FORM)

### NAND REALIZATION OF THE REDUCED LOGIC EXPRESSION

# **OBSERVATIONS**

| A | B | С | D | Expected Output | Observed                  | d Output             |

|---|---|---|---|-----------------|---------------------------|----------------------|

|   |   |   |   | / Jo /          | For simplified expression | For NAND realization |

| 0 | 0 | 0 | 0 | 181             |                           |                      |

| 0 | 0 | 0 | 1 | 7.4             |                           |                      |

| 0 | 0 | 1 | 0 | 5               |                           |                      |

| 0 | 0 | 1 | 1 |                 | ALAC                      |                      |

| 0 | 1 | 0 | 0 |                 |                           |                      |

| 0 | 1 | 0 | 1 |                 |                           |                      |

| 0 | 1 | 1 | 0 |                 |                           |                      |

| 0 | 1 | 1 | 1 |                 |                           |                      |

| 1 | 0 | 0 | 0 |                 |                           |                      |

| 1 | 0 | 0 | 1 |                 |                           |                      |

| 1 | 0 | 1 | 0 |                 |                           |                      |

| 1 | 0 | 1 | 1 |                 |                           |                      |

| 1 | 1 | 0 | 0 |                 |                           |                      |

| 1 | 1 | 0 | 1 |                 |                           |                      |

| 1 | 1 | 1 | 0 |                 |                           |                      |

| 1 | 1 | 1 | 1 |                 |                           |                      |

# EXERCISE

1. Simulate the simplified expression implemented in lab using Electronics Workbench or any other simulation tool and generate its NAND equivalent using *Logic Converter* tool. Attach hardcopy of the simulated circuit/output here.

# Lab Session 04

### **OBJECTIVE**

Implementing half and full adder circuits.

# **COMPONENTS AND APPARATUS REQUIRED**

- Digital logic trainer board or the following components: Bread board, 5 V - Power Supply, Multimeter, LEDs with Resistors, Switches

- 2. Logic probe

- 3. Connecting wires

- 4. Following ICs and their datasheets or pin configurations:

- 5. 7408 Quad 2-input AND Gate

- 6. 7432 Quad 2-input OR Gate

- 7. 7486 Quad 2-input XOR Gate

# THEORY

### Half Adder

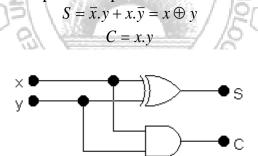

A combination circuit that performs the addition of two bits without accounting for the previous carry is called half adder. It needs two binary inputs and two binary outputs. The input variables designate the augend and addend bits. The output variables produce the sum and carry. The simplified sum of product expressions for a half adder are:

NGINER

Figure 1: Logic circuit for Half Adder

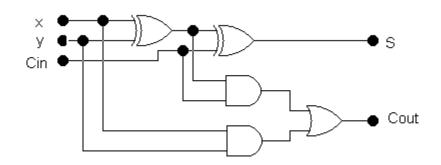

#### **Full Adder**

A combinational circuit that performs the addition of three input bits. It consist of three inputs and two outputs. Two of the input variables, represent the two significant bits to be added. The third input, represents the carry from the previous lower significant position. The output variables produce the sum and carry. The simplified sum of product expressions for a half adder are:

$$S = \overline{x}.\overline{y}.z + \overline{x}.y.\overline{z} + x.\overline{y}.\overline{z} + x.y.z = x \oplus y \oplus z$$

$$C = y.x + x.z + y.z = (x \oplus y).z + x.y$$

Figure 2: Circuit diagram for Full Adder

# HARDWARE IMPLEMENTATION AND OBSERVATIONS

Implement the half adder and full adder circuits in hardware (refer to appendix A for IC pin configurations) and record the observations in the following tables:

|     | Half Adder |                   |         |       |        | 1       | Full Add | er    |     |     |      |

|-----|------------|-------------------|---------|-------|--------|---------|----------|-------|-----|-----|------|

| Inp | Inputs     |                   | Outputs |       | Inputs |         | Inputs   |       |     | Out | puts |

| X   | Y          | Carry             | Sum     | ENG   | X      | y~      | z        | Carry | Sum |     |      |

| 0   | 0          |                   | 1.0     |       | 0      | 0       | 0        |       |     |     |      |

| 0   | 1          |                   | -12/    | ~7    | 0      | 0       | 1        |       |     |     |      |

| 1   | 0          | $\langle \rangle$ | 2//     | S     | 0      | > 1/2   | 0        |       |     |     |      |

| 1   | 1          |                   | 1151    |       | 0      | 1/2     | 1        |       |     |     |      |

|     |            |                   | N       | 1.11  | 1      | 0       | - 0      |       |     |     |      |

|     |            |                   | ZI \    | 18000 | 1      | 0       | 1        |       |     |     |      |

|     |            |                   | PI      |       | 1      | 8 /1 /E | 0        |       |     |     |      |

|     |            | 5                 | -81 1   |       | 1      | 1/2     | 71       |       |     |     |      |

# **EXERCISES**

1. Design a full subtractor circuit and simulate it using Electronic Workbench or any simulation tool. Compare the results of simulation with that of your designed circuit. Attach hardcopy of the simulated circuit/output here.

KARACH

# Lab Session 05

#### **OBJECTIVE**

Simulating a 4-bit parallel adder on Electronics Workbench

#### THEORY

#### **4-Bit Parallel Adder**

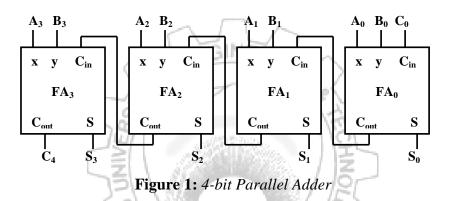

A 4-bit parallel adder can add two 4-bit values. One way of constructing such an adder is to simply cascade four full adders as shown in figure 1. Here  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$  are two 4-bit values to be added. FA3, FA2, FA1 and FA0 are the four full adders that are cascaded in parallel to provide the desired result.  $S_3S_2S_1S_0$  is the final 4-bit sum.  $C_0$  is the external carry input (if any) to the circuit and  $C_4$  is the final carry generated by the 4-bit addition.

#### **Creating Subcircuits in Electronic Workbench**

Creating a subcircuit allows you to reuse the circuit multiple times in a design and in future designs. Subcircuits may contain basic circuit elements or other subcircuit definitions. To create a subcircuit in Electronics Workbench:

- 1. First you have to design the circuit that you want to implement. Let's say you want to create a half-adder, so you simply draw a circuit with a XOR and AND gate (XOR is SUM and AND is Carry Out).

- 2. Select all components of the design that needs to be included in the subcircuit.

- 3. From the menu *Circuit*, select *Create Subcircuit*. Type a name and choose appropriate options. This will open a subwindow on the main design area containing the initially selected components.

- 4. Drag the input and output lines towards the edges to make input and output ports/terminals in the subcircuit.

- 5. Now click anywhere in the outer design area, this will close the internal structure of the subcircuit. The subcircuit will appear as a block on the main design area with assigned input and output lines. Now this block can be replicated (copy-pasted) where ever required or can be saved for future reuse.

#### LDST

NED University of Engineering & Technology – Department of Computer & Information Systems Engineering

#### PROCEDURE

- 1. Create a subcircuit for a full adder unit. Refer to lab session 6 for the gate level circuit of a full adder. This subcircuit should have three inputs namely x, y, C<sub>in</sub> and two outputs namely C<sub>out</sub> and S.

- 2. Replicate the subcircuit to make a total of four full adder subcircuits namely FA3, FA2, FA1 and FA0.

- 3. Make connections among these full adders as shown in figure 1.

- 4. Again create a subcircuit containing all these four full adders to make a single unit of a 4bit parallel adder. This new subcircuit should have nine inputs (C<sub>0</sub>, A3, A<sub>2</sub>, A<sub>1</sub>, A<sub>0</sub>, B<sub>3</sub>, B<sub>2</sub>, B<sub>1</sub>, B<sub>0</sub>) and five outputs (C<sub>4</sub>, S<sub>3</sub>, S<sub>2</sub>, S<sub>1</sub>, S<sub>0</sub>).

- 5. Connect the inputs to switches and outputs to indicators. Apply various combinations of 1s and 0s at inputs and check the binary values at the outputs.

#### **EXERCISES**

1. Find the sum and output carry for the addition of following two 4-bit numbers if the input carry  $C_0 = 0$ .

| a. | $A_3A_2A_1A_0 = 110$ | $B_3B_2B_1$    | $B_3B_2B_1B_0 = 1101$                  |        |                |  |

|----|----------------------|----------------|----------------------------------------|--------|----------------|--|

|    | C <sub>4</sub>       | S <sub>3</sub> | S <sub>2</sub>                         | $S_1$  | S <sub>0</sub> |  |

|    |                      | N/E!           | GINEER                                 | $\sim$ |                |  |

|    |                      | 105            | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |        |                |  |

| b. | $A_3A_2A_1A_0 = 1011$ $B_3B_2B_1B_0 = 1010$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |  |  |

|----|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

|    | C <sub>4</sub>                              | S <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | S <sub>2</sub>                                                                                                  | $S_1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S <sub>0</sub> |  |  |

|    |                                             | 1道/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | and the state of the | 1 lor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |  |  |

|    |                                             | and the second s |                                                                                                                 | and the second s |                |  |  |

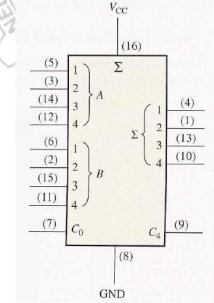

2. Using the logical symbol of parallel adder (given below) realize 2's complement adder/subtractor unit.

3. Test the designed circuit in Q2 for the given values of A and B when  $C_0 = 0$ .

| a. | $A_3A_2A_1A_0 = 101$ | $1 \qquad B_3B_2B_1$ | $B_0 = 1101$ |                |                |

|----|----------------------|----------------------|--------------|----------------|----------------|

|    | C <sub>4</sub>       | $S_3$                | $S_2$        | S <sub>1</sub> | S <sub>0</sub> |

|    |                      |                      |              |                |                |

# Lab Session 06

# **OBJECTIVE**

Experimenting with digital decoder IC.

# COMPONENTS AND APPARATUS REQUIRED

- 1. Digital logic trainer board or the following components:

- Bread board, 5 V Power Supply, Multimeter, LEDs with Resistors, Switches

- 2. Logic probe

- 3. Connecting wires

- 4. Following ICs and their datasheets or pin configurations:

- 5. 74138 3 x 8 Line Decoder / Demultiplexer

# THEORY

#### Decoder

A Decoder is a combinational circuit that converts binary information from n input lines to a maximum of  $2^n$  unique output lines. In practical applications, decoders are often used for selecting one of several devices.

# Demultiplexer

A Demultiplexer (DMUX) is a circuit that receives information on a single line and transmits this information on one of  $2^n$  possible output lines. The selection of a specific output line is controlled by the bit values of n selection lines. A decoder with an enable input can function as a Demultiplexer (DMUX).

# 74138 - 3 x 8 Line Decoder / Demultiplexer

The 74138 IC has three inputs and eight output lines. It has three enable inputs and for the IC to function all three inputs need to be enabled. Refer to appendix A for IC pin configuration. Function of various pins of this IC is described below:

- Y0 through Y7: Active low data outputs

- *A*, *B*, *C*: Active high input / select lines with C being the MSB

- *G1:* Active high enable Input

- G2A' and G2B': Active low enable Inputs

- VCC and GND: Supply connections lines

# **TESTING PROCEDURE AND OBSERVATIONS**

- 1 Make Vcc and Gnd supply connections.

- 2 Connect the three inputs A, B and C to switches.

- 3 Set appropriate values at enable inputs to activate the IC.

- 4 Apply different combinations of 1s and 0s at data inputs.

- 5 Observe the output and record your observations in the following table.

| С | B | A | YO | Y1 | Y2 | <i>Y3</i> | <i>Y4</i> | <i>Y</i> 5 | Y6 | <i>Y</i> 7 |

|---|---|---|----|----|----|-----------|-----------|------------|----|------------|

| 0 | 0 | 0 |    |    |    |           |           |            |    |            |

| 0 | 0 | 1 |    |    |    |           |           |            |    |            |

| 0 | 1 | 0 |    |    |    |           |           |            |    |            |

| 0 | 1 | 1 |    |    |    |           |           |            |    |            |

| 1 | 0 | 0 |    |    |    |           |           |            |    |            |

| 1 | 0 | 1 |    |    |    |           |           |            |    |            |

| 1 | 1 | 0 |    |    |    |           |           |            |    |            |

| 1 | 1 | 1 |    |    |    |           |           |            |    |            |

#### **EXERCISES**

- 1. What will be the binary values at the outputs, Y0 through Y7, of 74138 if:

- All three enable pins are connected to ground?

- All three enable pins are connected to VCC?

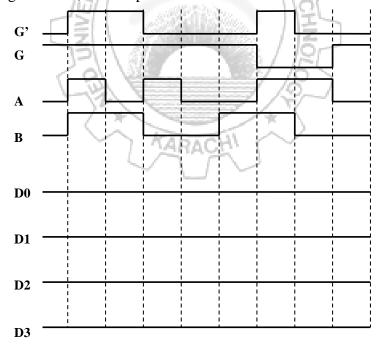

- Consider a 2 x 4 Decoder with two enable inputs (one active high G and one active low G'). Draw the output wave-forms for D0, D1, D2 and D3, if the two select inputs are A and B (B being the MSB). All outputs are active low.

- 3. Cascade two 2x4 decoders to form a 3x8 decoder.

- a. Implement the circuit in hardware using two 74138 ICs and observe the output.

- **b.** Simulate the circuit on Electronics Workbench or any other simulation software using 74139 dual 2-line-to-4-line decoder/demultiplexer IC. Attach hardcopy of the simulated circuit/output here.

# Lab Session 07

#### **OBJECTIVE**

#### Experimenting with digital multiplexer IC.

#### COMPONENTS AND APPARATUS REQUIRED

- 1. Digital logic trainer board or the following components: Bread board, 5 V - Power Supply, Multimeter, LEDs with Resistors, Switches

- 2. Logic probe

- 3. Connecting wires

- 4. Following ICs and their datasheets or pin configurations:

- 5. 74150 16 x 1 Mutiplexer

# THEORY

#### **Multiplexers**

A digital data Multiplexer (MUX) is a combinational circuit having several data inputs and a single output. A set of *data-select* inputs is used to control which of the data inputs is routed to the single output. A multiplexer is also called a *data selector* because of this ability to select which data input is connected to the output. Normally there are  $2^n$  input lines and n selection lines whose bit combination determine which input is selected.

GINEE

# 74150 - 16 x 1 Multiplexer

The 74150 IC has sixteen data inputs and four data-selection lines. It also contains an active low enable and an active low output line. Refer to appendix A for IC pin configuration. Function of various pins of this IC is described below:

- E0 through E15: Active high data input lines

- A, B, C, D: Active high data select lines with D being the MSB

- *W*: Active low output line

- *G*': Active low enable line

- VCC and GND: Supply connections lines

# **TESTING PROCEDURE AND OBSERVATIONS**

- 1 Make Vcc and Gnd supply connections.

- 2 Connect the data select inputs A, B, C and D to switches.

- 3 Set appropriate values at enable inputs to activate the IC.

- 4 Connect the data inputs E0 through E15 to switches. For simplicity just two or three data inputs can be connected to switches at a time. Remaining inputs will draw 1 by default (float high characteristic of TTL ICs).

- 5 Now select any data input with the help of data selectors A, B, C, and D. Apply different data (1 or 0) at this selected data inputs.

- 6 Observe the output. The invert of the value applied at the selected data input will appear at the output.

7 Record your observations for the input configurations given in the following table. Here only E0, E4 and E15 data inputs are considered.

| G' | D | С | B | A | Value at<br>data input | W | G' | D | С | B | A | Value at<br>data input | W |

|----|---|---|---|---|------------------------|---|----|---|---|---|---|------------------------|---|

| 0  | 0 | 0 | 0 | 0 |                        |   | 0  | 1 | 0 | 0 | 1 |                        |   |

| 0  | 0 | 0 | 0 | 1 |                        |   | 0  | 1 | 0 | 1 | 0 |                        |   |

| 0  | 0 | 0 | 1 | 0 |                        |   | 0  | 1 | 0 | 1 | 1 |                        |   |

| 0  | 0 | 0 | 1 | 1 |                        |   | 0  | 1 | 1 | 0 | 0 |                        |   |

| 0  | 0 | 1 | 0 | 0 |                        |   | 0  | 1 | 1 | 0 | 1 |                        |   |

| 0  | 0 | 1 | 0 | 1 |                        |   | 0  | 1 | 1 | 1 | 0 |                        |   |

| 0  | 0 | 1 | 1 | 0 |                        |   | 0  | 1 | 1 | 1 | 1 |                        |   |

| 0  | 0 | 1 | 1 | 1 |                        |   | 1  | 0 | 1 | 0 | 1 |                        |   |

| 0  | 1 | 0 | 0 | 0 |                        |   | 1  | 1 | 0 | 1 | 0 |                        |   |

### EXERCISES

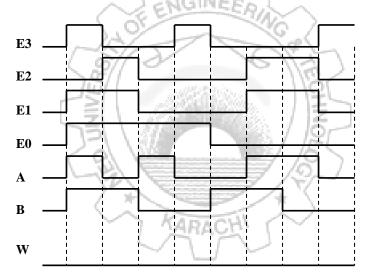

1. Consider 4x1 Multiplexer. Draw the output wave-form for the following data inputs (E<sub>0</sub>, E<sub>1</sub>, E<sub>2</sub>, E<sub>3</sub>,) and select lines A, B (B being the MSB). Output is W.

2. Implement the following function using 8x1 multiplexer.

$$F(A, B, C, D) = \sum (1,3,5,6,9,13,15)$$

- a. Implement the circuit in hardware using 74150 IC and observe the output.

- b. Simulate the circuit on Electronics Workbench or any other simulation software using 74151 8-line-to-1-line multiplexer IC. Attach hardcopy of the simulated circuit/output here.

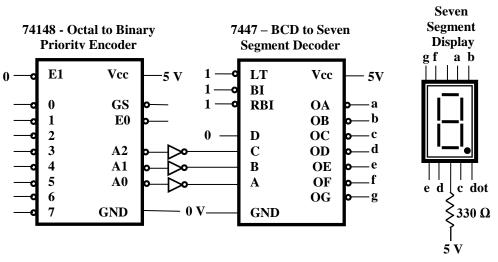

# Lab Session 08

# **OBJECTIVE**

Experimenting with encoder and seven segment display driver ICs.

# COMPONENTS AND APPARATUS REQUIRED

- 1. Digital logic trainer board or the following components: Bread board, 5 V - Power Supply, Multimeter, LEDs with Resistors, Switches

- 2. Logic probe

- 3. Connecting wires

- 4. Seven Segment Display (Common Anode Type) with resistor

- 5. Following ICs and their datasheets or pin configurations:

- 6. 74148 Octal to Binary Priority Encoder

- 7. 7447 BCD to Seven Segment Driver

- 8. 7404 hex inverter

# THEORY

#### Encoder

An Encoder is a digital function that produces a reverse operation from that of a decoder. An Encoder has  $2^n$  (or less) input lines and n output lines. The output lines generate the binary code for the  $2^n$  input variables.

GINER

# **Priority Encoder**

A simple encoder may produce an erroneous output if more than one of its inputs is high. A Priority Encoder is one that responds to just one input among those that may be simultaneously high, in accordance with some priority system. The most common priority system is based on the relative magnitudes of the inputs: whichever decimal input is largest is the one that is encoded.

# 74148 8 x 3 Octal to Binary Priority Encoder

The 74148 is a priority encoder with active-low inputs for decimal digits. There are nine inputs lines (including an enable input) and five output lines, of which three represents the binary code for the octal digit. Refer to appendix A for IC pin configuration. Function of various pins of this IC is described below:

- *0 through 7:* Active low data inputs representing the octal digits

- A2, A1, A0: Active low output lines representing the binary code

- *E1:* Active low enable Input

- *E0:* Active low output indicating none of the inputs is high

- GS: Active low output indicating any of the inputs is high

- VCC and GND: Supply connections lines

# 7447 BCD to Seven Segment Driver

7447 IC is particularly used to drive common-anode Seven Segment displays. Its input is a BCD number and output drives a seven segment display. Refer to appendix A for IC pin configuration. Function of various pins of these ICs is described below:

- *A*, *B*, *C*, *D*: Active high inputs representing BCD digits (D being the MSB).

- *OA through OG:* Active low outputs to drive segments *a* through *g* of the display.

- *RBI*: Ripple Blanking Input. Turns off all the segments if kept low, provided that LT is kept high and all other inputs (A, B, C, D, BI) are kept low. Should be kept high otherwise.

- **BI / RBO:** Wire-AND logic serving as a Blanking Input and / or Ripple Blanking Output.

- BI: Turns off all the segments if low.

- *RBO:* Goes to a low level (response condition) along with other outputs, when RBI and inputs A, B, C, and D are low with LT input at high level.

- *LT*: Lamp Test input. Tests whether all segments are working or not. Illuminates all segments if kept low, provided that BI is kept high. Should be kept high otherwise.

- VCC and GND: Supply connections lines

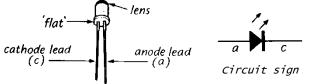

# Seven Segment Displays

A Seven Segment Display consists of seven light-emitting segments. The segments are designated by letters a through g (see figure 1). By illuminating various combinations of segments, the numerals 0 through 9 can be displayed. Seven Segment Displays are commonly constructed with light-emitting diodes (LEDs) and with liquid-crystal displays (LCDs). LEDs generally provide greater illumination levels but require much greater power than LCDs.

An LED display can be a common-anode type or common cathode type. In common anode type, a high voltage is applied at the *common* terminal of the display and low voltage is applied at a segment's terminal for illumination. In the common-cathode type, a low voltage is applied at the *common* terminal of the display and high voltage is applied at a segment's terminal of the display and high voltage is applied at a segment's terminal of the display and high voltage is applied at a segment's terminal for illumination.

Figure 1: Seven Segment Display

# IMPLEMENTATION AND OBSERVATIONS

You are required to display the outputs of a 74148 encoder IC on a seven segment display. The circuit is given in figure 2.

- 1 Make connections as shown in figure 2. (refer to appendix A for IC pin configurations).

- 2 Select any input from 74148 IC and observe the corresponding decimal code being displayed on the seven segment.

Figure 2: Circuit for displaying encoders output on 7-segment display

# EXERCISES

1. Perform the Lamp Test for the designed circuit and write your observations.

2. How can you use 7447 IC to drive a common-cathode display?

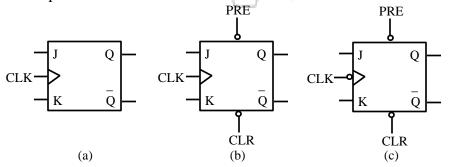

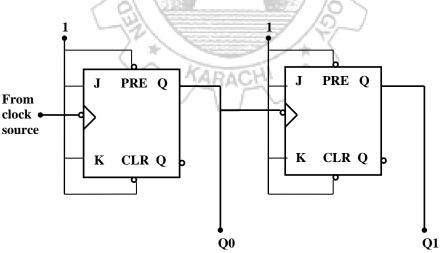

# Lab Session 09

#### **OBJECTIVE**

#### Testing different modes of JK flip flop and implementing a modulo-4 asynchronous upcounter using JK flip flops

#### **COMPONENTS AND APPARATUS REQUIRED**

- 1. Digital logic trainer board or the following components:

- Bread board, 5 V Power Supply, Multimeter, LEDs with Resistors, Switches

- 2. Logic probe

- 3. Connecting wires

- 4. Following ICs and their datasheets or pin configurations:

- 5. 7473 / 7476 JK Flip-Flop

# THEORY

#### Flip-Flop

A flip-flop circuit can maintain a binary state indefinitely (as long as the power is delivered to the circuit) until directed by an input signal to switch states. The major differences among various types of flip-flops are in the number of inputs they possess and in the manner in which the inputs affect the binary state.

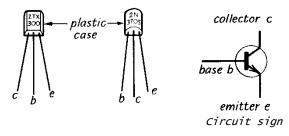

# JK Flip-Flop

JK flip flop is an edge triggered device. A typical JK flip flop has three inputs: J, K and a clock input. The flip-flop can be either positive or negative edge triggered. The output Q is available in complemented form as well.

Figure 1: Symbol for JK flip-flop.

(a) Positive-edge triggering. (b) Active low Preset (PRE) and Clear (CLR) with positive-edge triggering. (c) Active low Preset (PRE) and Clear (CLR) with negative-edge triggering

Besides the usual inputs and output, most of the flip-flop IC also possess two asynchronous inputs, namely *Preset* and *Clear*. These inputs are usually active low. If used, *Preset* and *Clear* inputs keep the flip-flop in set and reset state respectively, irrespective of the other

inputs. Both of these inputs cannot be used simultaneously, otherwise they will bring the flipflop in unstable state.

# 7473 / 7476 Dual JK Flip Flop

Both the ICs 7473 and 7476 are similar in functionality except for one difference. The flipflops in 7473 have only one type of active low asynchronous input, which is the *Clear* input, whereas the flip-flops in 7476 have both *Preset* and *Clear* inputs. Both these ICs have negative edge triggered flip-flops. Refer to appendix A for IC pin configuration Function of various pins of this IC is described below:

- 1CLK, 2CLK: Negative edge triggered clock inputs for FF1 and FF2 respectively.

- 1PRE, 2PRE(for 7476 only): Active low preset inputs for FF1 and FF2 respectively.

- 1CLR, 2CLR: Active low clear inputs for FF1 and FF2 respectively.

- 1J, 2J: Active high J inputs for FF1 and FF2 respectively.

- 1K, 2K: Active high K inputs for FF1 and FF2 respectively.

- *1Q, 2Q:* Active high outputs for FF1 and FF2 respectively.

- 1Q', 2Q': Active low outputs for FF1 and FF2 respectively.

- VCC and GND: Supply connections lines

# **Digital Counters**

A digital counter is a set of flip-flops whose states change in response to pulses applied at the input to the counter. Every counter resets after a certain number of clock pulses. Thus, as it name implies, a counter is used to count pulses. An n stage counter can count up to a maximum of  $2^n$  states. n is equal to the number of flip-flops required for the construction of counter.

# **Modulus Counters**

The number of input pulses that causes a counter to reset to its initial count is called the *modulus* of the counter. Thus, the modulus equals to total number of distinct *states* (counts), including zero that a counter can store. A binary counter with *n* stages is a *modulo*- $2^n$  (or *MOD*- $2^n$ ) counter. The largest count a *mod*-*N* counter can achieve is *N*-1, i.e. a *mod*-*N* counter never reaches the binary number equal to its modulus. N is always equal to or less than  $2^n$ .

ARACH

Counters can be classified as:

- *Synchronous Counters*, which are clock driven. All the flip-flops are driven by a single clock.

- *Asynchronous Counters*, which are event driven. Clock input is given to the first flip-flop only. Rest of the flip-flops are driven by their preceding flip-flops.

# **Mod-4 Asynchronous Up Counter**

The number of flip-flops required to construct a mod-4 counter is 4. This counter will count from 0 to 3, a total of 4 distinct states.

# **TESTING PROCEDURE AND OBSERVATIONS**

# 7473 / 7476 Dual JK Flip Flop

- 1 Make Vcc and Gnd supply connections.

- 2 Connect the CLK input to some clock source or a switch.

- 3 Apply different combinations of 1s and 0s at inputs J, K, Preset and Clear.

- 4 Observe the output and record your observations in the following table.

| CLK          | PRE* | CLR | J  | K | Q |

|--------------|------|-----|----|---|---|

| $\downarrow$ | 1    | 1   | 0  | 0 |   |

| $\downarrow$ | 1    | 1   | 0  | 1 |   |

| $\downarrow$ | 1    | 1   | 1  | 0 |   |

| $\downarrow$ | 1    | 1   | 1  | 1 |   |

| $\downarrow$ | 1    | 0   | 1  | 1 |   |

| $\downarrow$ | 0    | 1/  |    | 1 |   |

| 1            | 1    | ME0 | K. | 1 |   |

\*ignore if 7473 IC is being used

# **MOD-4** Asynchronous Counter

- 1 Make connections as shown in figure 2. (refer to appendix A for IC pin configurations).

- 2 Observe the binary values at the outputs of the two flip flops with the incoming clock pulses.

Figure 2: MOD-4 Asynchronous Counter

# **EXERCISES**

1. Draw the timing diagram for MOD-4 counter designed in this laboratory session.

- 2. Simulate MOD-5 asynchronous counter using Electronic Workbench or any other simulation tool. The number of flip-flops required to construct a MOD-5 counter is 3. This counter will count from 0 to 4, a total of 5 distinct states. Since a 3-stage counter can count up to 8 states at maximum, a NAND gate is used to reset it after 5 clock pulses. Attach hardcopy of the simulated circuit/output here.

- 3. Draw the timing diagram for MOD-5 counter simulated in exercise 2.

# Lab Session 10

# **OBJECTIVE**

#### Experimenting with decade counter IC.

# COMPONENTS AND APPARATUS REQUIRED

- 1. Digital logic trainer board or the following components: Bread board, 5 V - Power Supply, Multimeter, LEDs with Resistors, Switches

- 2. Logic probe

- 3. Connecting wires

- 4. Following ICs and their datasheets or pin configurations:

- 5. 7490 decade counter

# THEORY

# 7490 Decade Counter

7490 decade counter can generate the following two sequences:

1. BCD sequence: In this case output QA is connected to input B, external clock is applied to input A

NGINFE

2. Bi-quinary sequence: In this case output QD is connected to input A, external clock is applied to input B

Refer to appendix A for IC pin configuration. Function of various pins of this IC is described below:

- Input A, Input B: Negative edge triggered clock inputs.

- QA, QB, QC and QD: Active high outputs.

- R91, R92, R01, R02: Active high reset inputs. These resets are activated as follows:

- VCC and GND: Supply connections lines.

|     | Reset . | Inputs |     | Output |     |     |    |  |

|-----|---------|--------|-----|--------|-----|-----|----|--|

| R01 | R02     | R91    | R92 | QD     | QC  | QB  | QA |  |

| Н   | Н       | L      | Х   | L      | L   | L   | L  |  |

| Н   | Н       | X      | L   | L      | L   | L   | L  |  |

| Х   | X       | Н      | Н   | Η      | L   | L   | Н  |  |

| Х   | L       | X      | L   |        | COU | JNT |    |  |

| L   | X       | L      | Х   |        | COU | JNT |    |  |

| L   | Х       | Х      | L   | COUNT  |     |     |    |  |

| Х   | L       | L      | Х   |        | COU | JNT |    |  |

# **TESTING PROCEDURE AND OBSERVATIONS**

- 1 Make Vcc and Gnd supply connections.

- 2 Disable all RESET inputs.

- 3 Connect input A and input B according to the connections indicated in the previous section to generate BCD count and then bi-quinary count.

- 4 Observe the output in each case and record your observations given in the following table.

|                | В  | CD Cou | nt     |       |          | Bi-quinary Count |    |    |    |    |  |  |

|----------------|----|--------|--------|-------|----------|------------------|----|----|----|----|--|--|

| Clock<br>Pulse | QD | QC     | QB     | QA    |          | Clock<br>Pulse   | QD | QC | QB | QA |  |  |

| 0              |    |        |        |       |          | 0                |    |    |    |    |  |  |

| 1              |    |        |        |       |          | 1                |    |    |    |    |  |  |

| 2              |    |        |        |       |          | 2                |    |    |    |    |  |  |

| 3              |    |        |        |       |          | 3                |    |    |    |    |  |  |

| 4              |    |        |        |       |          | 4                |    |    |    |    |  |  |

| 5              |    |        |        |       |          | 5                |    |    |    |    |  |  |

| 6              |    |        |        |       |          | 6                |    |    |    |    |  |  |

| 7              |    |        |        | ~     | <i>[</i> | 7~               |    |    |    |    |  |  |

| 8              |    |        |        | Lai   | ŚПМ      | - 8              |    |    |    |    |  |  |

| 9              |    |        | $\sim$ | 8 222 |          | 9                | 2  |    |    |    |  |  |

| 10             |    |        | X      | ~     | -        | 10               | 5  |    |    |    |  |  |

# **EXERCISES**

- 1. Enable the RESET inputs RO1 and RO2 (keeping R91 and R92 disabled) and write your observations below:

- 2. Enable the RESET inputs R91 and R92 (keeping R01 and R02 disabled) and write your observations below:

- 3. Enable all the RESET inputs R01, R02, R91 and R92 and write your observations below:

# Lab Session 11

# **OBJECTIVE**

#### Designing and simulating the seconds section of a digital clock

# THEORY

# **Digital Clock**

A digital clock is a time keeping circuit that displays seconds, minutes and hours. For seconds' section of a digital clock, a MOD-60 counter needs to be designed. A simple way to do this is to design MOD-10 and MOD-6 counters separately and then cascade them.

# Generating Clock (Square Wave) Signals for Sequential Circuits in Electronic Workbench

Most sequential circuits require trigger/pulse for the functioning of their memory elements. This trigger is merely a 0 to1 or 1 to 0 signal transition at the input where it needs to be applied. This can be achieved by simply connecting a switch which can toggle between 0 and 1.

For continuous pulse generation a proper clock source is needed. In EWB, this can be achieved via function generator (in *Instruments Parts Bin*) or more easily as follows:

- 1. From the *Sources Parts Bin*, drag and drop *Clock* on the design area. Double click the *Clock* to reveal the properties dialog box, where frequency, duty cycle and voltage of the signal can be chosen.

- 2. Connect the negative end of the component to the ground.

- 3. Positive end can be connected to the point where the clock signal needs to be applied. You can connect an indicator here to view the generated signal.

# PROCEDURE

In this lab session we will use two 7490 ICs to design MOD-10 and MOD-6 counters.

- 1. For MOD-10 counter, connect a 7490 IC in BCD count mode refer to previous lab session. Disable all RESET inputs and apply clock at input A as illustrated is the previous section. Set the frequency of the clock to 1 Hz.

- 2. Connect another 7490 IC in BCD mode. To convert it to MOD-6 counter, connect R01 to QB and R02 to QC. This will activate the resets of 7490 when it reaches the count of 6. Disable the other two RESET inputs R91 and R92. Now connect QD of the MOD-10 counter created in the last step to the clock input (input A) of this IC. QD is the MSB of the MOD-10 count and it goes from 1 to 0 only when the counter resets after 9, thus providing the negative edge to increment the MOD-6 counter. Here also a seven segment display can be connected to view the outputs. Now collectively this circuit works as a MOD-60 counter.

3. The output of this circuit can be viewed on seven segment displays. Two kinds of 7 segment displays are available in EWB. One takes four BCD inputs directly and the other one takes seven inputs for the seven segments. The later one is connected via a BCD to seven segment converter. For our application the former one is simpler to use as it provides the BCD to seven segment conversion internally.

# EXERCISES

1. Design the hours' section of a digital clock on EWB. The clock should be a 24 hour clock. Attach hardcopy of the simulated design here.

# Lab Session 12

# **OBJECTIVE**

Experimenting with bidirectional universal shift register IC

# COMPONENTS AND APPARATUS REQUIRED

- Digital logic trainer board or the following components: Bread board, 5 V - Power Supply, Multimeter, LEDs with Resistors, Switches

- 2. Logic probe

- 3. Connecting wires

- 4. Following ICs and their datasheets or pin configurations:

- 5. 74194 4-bit bidirectional universal shift register

# THEORY

#### **Shift Registers**

A Register is a set of flip-flops used to store binary data. A register, which is capable of shifting its binary information either to the right or left, is called a shift register. The logical configuration of a register consists of a chain of flip-flops connected in cascade, with the output of one flip-flop connected to the input of next flip-flop. All flip-flops receive a common clock pulse, which causes the shift from one stage to the next.

GINER

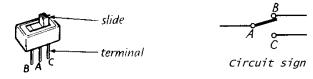

# **Universal Bidirectional Shift Registers**

A bi-directional shift register is one whose bits can be shifted from left to right or from right to left. A universal shift register is a bi-directional register whose input can be in either serial or parallel form and whose output can be in either serial or parallel form.

# 74194 4-Bit Bidirectional Universal Shift Register

The 74194 register provides parallel as well as serial loading in both directions. A, B, C, and D are inputs for parallel loading, whereas SR and SL are inputs for serial loading with right or left shifting respectively. S1 and S0 are used to select the loading mode. Refer to appendix A for IC pin configuration. Function of various pins of this IC is described below:

- A, B, C and D: Active high inputs for parallel loading.

- QA, QB, QC and QD: Active high outputs.

- *S0 and S1:* Active high mode control inputs. The following table shows combinations of S1 and S0 to enable various modes.

| <i>S1</i> | <i>S0</i> | Clock | Action        |

|-----------|-----------|-------|---------------|

| 0         | 0         | Х     | No change     |

| 0         | 1         | 1     | Shift right   |

| 1         | 0         | ↑     | Shift left    |

| 1         | 1         | 1     | Parallel load |

- *SR*: Active high serial input for right shifting.

- *SL:* Active high serial input for left shifting.

- *CLR:* Active low clear input.

- *CLK:* Positive edger triggered cock input.

- VCC and GND: Supply connections lines.

# **TESTING PROCEDURE AND OBSERVATIONS**

- 1 Make Vcc and Gnd supply connections.

- 2 Connect the CLK input to some clock source or a switch.

- 3 Disable CLR input.

- 4 Apply different combinations of 1s and 0s at inputs J, K, Preset and Clear.

- 5 Observe the output and record your observations given in the following table.

| <i>S1</i> | <i>S0</i> | SL | SR | $\boldsymbol{A}$        | B   | С | D   | QA     | QB                | QC | QD |

|-----------|-----------|----|----|-------------------------|-----|---|-----|--------|-------------------|----|----|

| 0         | 0         | 0  | 1  | 0                       | 0   | 0 | 0   |        |                   |    |    |

| 0         | 1         | 1  | 0  | .0                      | 0   | 0 | Eb, | 5      |                   |    |    |

| 1         | 0         | 0  | 0  | $\left\{ 0, 0 \right\}$ | 0   | 1 | 0   | ,<br>G |                   |    |    |

| 1         | 1         | 0  | 0  | /0 /                    | 0   | 1 | Ť   | 5      |                   |    |    |

| 0         | 0         | 1  | 1  | 0                       | d - | 0 | 0   | 2      | $\langle \rangle$ |    |    |

| 0         | 1         | 1  | 1  | 0                       | 1   | 0 | 1   | 18     | i                 |    |    |

| 1         | 0         | 1  | 0  | 0                       | 1   | 1 | 0   |        | 2                 |    |    |

| 1         | 1         | 1  | 0  | 0                       | 1   | 1 | 1   |        |                   |    |    |

| 1         | 1         | 0  | 0  | 2 1                     | 1   | 1 | 1   | 1 12   | ×[                |    |    |

#### **EXERCISES**

1. Show connections of 74194 to convert it into a ring counter with right shifting.

|   | CLR | Vcc  | 16 |

|---|-----|------|----|

| 2 | SR  | QA   | 15 |

| 3 | A   | QB   | 14 |

| 4 | В   | QC   | 13 |

| 5 | C   | QD   | 12 |

| 6 | D   | CLK< | 11 |

| 7 | SL  | S1   | 10 |

| 8 | GND | S0   | 9  |

|   |     |      |    |

74194

# Lab Session 13

# **OBJECTIVE**

Designing and implementing a 3-bit even sequence synchronous up counter using T flip flops

# COMPONENTS AND APPARATUS REQUIRED

- 1. Digital logic trainer board or the following components:

- Bread board, 5 V Power Supply, Multimeter, LEDs with Resistors, Switches

- 2. Logic probe

- 3. Connecting wires

- Following ICs and their datasheets or pin configurations:

7473 / 7476 JK Flip-Flop

# THEORY

Synchronous counters are clock driven counters. It is a sequential circuit, the design of which involves the following steps:

- 1. Generate a state diagram and/or a state table from the statement of the problem.

- 2. Select the type of flip-flop for the circuit and generate the flip flop input equations needed for the required state transitions

- 3. Derive logic equations for generation of the output from the inputs and current state.

- 4. Generate a logic diagram of the circuit using ANDs, ORs, inverters, and flip flops.

# 3-bit Even Sequence Synchronous Up Counter

A 3-bit even sequence synchronous up counter will count through the following sequence: 0, 2, 4, 6 and repeat. The number of flip-flops required to construct such a counter is 3. The state of the flip flops is the final output of the circuit, therefore no explicit output equations need to be generated.

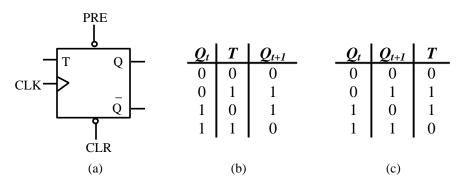

# T Flip-Flop

Figure 1: *T Flip Flop.* (a) Graphical symbol. (b) Characteristic table. (c) Excitation table